# Improving the Electrical Properties of Lanthanum Silicate Films on Ge Metal Oxide Semiconductor Capacitors by Adopting Interfacial Barrier and Capping Layers

Yu Jin Choi,<sup>†</sup> Hajin Lim,<sup>†,‡</sup> Suhyeong Lee,<sup>†</sup> Sungin Suh,<sup>†</sup> Joon Rae Kim,<sup>†</sup> Hyung-Suk Jung,<sup>†,‡</sup> Sanghyun Park,<sup>†</sup> Jong Ho Lee,<sup>†</sup> Seong Gyeong Kim,<sup>†</sup> Cheol Seong Hwang,<sup>\*,†</sup> and HyeongJoon Kim<sup>\*,†</sup>

<sup>†</sup>Department of Materials Science and Engineering & Inter-university Semiconductor Research Center, Seoul National University, Seoul 151-744, South Korea

<sup>‡</sup>System-LSI Division, Samsung Electronics Co. Ltd, Gyeonggido 446-712, South Korea

**ABSTRACT:** The electrical properties of La-silicate films grown by atomic layer deposition (ALD) on Ge substrates with different film configurations, such as various Si concentrations,  $Al_2O_3$ interfacial passivation layers, and  $SiO_2$  capping layers, were examined. La-silicate thin films were deposited using alternating injections of the  $La[N{Si(CH_3)_3}_2]_3$  precursor with  $O_3$  as the La and O precursors, respectively, at a substrate temperature of 310 °C. The Si concentration in the La-silicate films was further controlled by adding ALD cycles of SiO<sub>2</sub>. For comparison,  $La_2O_3$  films were also grown using  $[La(^{i}PrCp)_3]$  and  $O_3$  as the La precursor and oxygen source, respectively, at the identical substrate temperature. The capacitance–voltage (C–V) hysteresis decreased with an increasing Si concentration in the La-silicate films, although the films showed a slight increase in the capacitance equivalent oxide thickness. The adoption of  $Al_2O_3$  at the interface as a passivation layer resulted in lower C–V hysteresis and a low leakage current density. The C–V hysteresis voltages of the La-silicate films with  $Al_2O_3$  passivation and

SiO<sub>2</sub> capping layers was significantly decreased to ~0.1 V, whereas the single layer La-silicate film showed a hysteresis voltage as large as ~1.0 V.

KEYWORDS: La-silicate, Ge-substrate, Al<sub>2</sub>O<sub>3</sub> barrier, SiO<sub>2</sub> capping, hysteresis

## I. INTRODUCTION

Scaling of conventional complementary metal oxide semiconductor (CMOS) transistors using Si as the channel material has driven the integrated circuit industry since the 1970s and is expected to reach its physical limit within the next decade.<sup>1,2</sup> Ge is a feasible candidate for replacing Si as the channel material in p-type metal oxide semiconductor field-effect transistors (MOSFETs) of the post-14-nm technology node because it has a higher hole mobility than Si.<sup>3-6</sup> Similar to SiO<sub>2</sub>/Si in Si-MOSFETs, GeO<sub>2</sub>/Ge has been generally regarded as the most appropriate interface in Ge-MOSFETs. Nonetheless, the lack of thermodynamic stability at the GeO<sub>2</sub>/Ge interface hampers the development of Ge-MOSFETs. Many previous studies have demonstrated that the GeO<sub>2</sub>/Ge interface degrades because of desorption of GeO upon thermal annealing above 400 °C under a vacuum or in ambient N2, owing to an interfacial reaction.<sup>7,8</sup> With atomic force microscopy and thermal desorption spectroscopy studies, the Ge substrate underneath the GeO<sub>2</sub> layer was consumed by the GeO desorption that was produced by a volatilization reaction between  $GeO_2$  and Ge (GeO<sub>2</sub> + Ge  $\rightarrow$  2GeO).<sup>7-10</sup> Recently, Wang et al. demonstrated an oxygen vacancy diffusion model as the mechanism of GeO volatilization by employing <sup>18</sup>O and <sup>73</sup>Ge isotope labeling experiments. In those experiments, GeO desorbed from the GeO<sub>2</sub> surface, but the desorption was

triggered by an interfacial reaction between Ge and GeO<sub>2</sub>. GeO formation was equivalent to the generation of oxygen vacancies  $(V_0)$  at the GeO<sub>2</sub>/Ge interface in this redox reaction. V<sub>0</sub> diffused to the GeO<sub>2</sub> surface, and desorption occurred at the surface of the GeO<sub>2</sub> film.<sup>11</sup> A typical example of electrical degradation by GeO desorption is the large hysteresis in the capacitance-voltage (C-V) curves, which is attributed to electrically active defects near the interface and inside the bulk high-k film.<sup>8</sup> In contrast, thermodynamic calculations have shown that  $GeO_2$  + Ge has a lower Gibbs free energy than 2GeO at a typical processing temperature and pressure (the desorption reaction  $\text{GeO}_2 + \text{Ge} \rightarrow 2\text{GeO}$  has a positive Gibbs free energy change), suggesting that effective isolation of the  $GeO_2/Ge$  system from the atmosphere could suppress the reaction at the interface.<sup>12,13</sup> Considering this factor, there could be two possible methods to solve the interfacial reaction problem; one is to adopt a capping layer to isolate the  $GeO_2/$ Ge from the atmosphere, and the other is to adopt an interfacial passivation layer (or barrier layer) to physically separate the GeO<sub>2</sub> and Ge. There have been many reports on various interfacial passivation layers, such as ultrathin Si capping layers

Received: February 27, 2014 Accepted: April 15, 2014 Published: April 15, 2014 on Ge substrates,  $^{14}$  Ge nitride interfacial layers,  $^{15,16}$   $Al_2O_3$  and  $LaAlO_3\,$  dielectric inter layers,  $^{17,18}\,$  and high-quality  $GeO_2\,$ interfacial layers formed by plasma oxidation or high pressure oxidation.<sup>19,20</sup> Among the various passivation techniques, a Si capping layer on a Ge substrate has drawn a great deal of attention because of its superior electrical performance. Cheng et al. reported that a Si capping layer on a Ge substrate retarded the GeO volatilization and suppressed the C-V hysteresis of the HfO<sub>x</sub>N<sub>y</sub> gate dielectric films in the MOS structure.<sup>21</sup> The decrease in the C-V hysteresis by the Si capping layer was explained by the Si-O bonds having larger Gibbs free energies and higher thermodynamic stabilities than the Ge-O bonds, such that the reaction between the oxide and Ge substrate could be efficiently suppressed.<sup>21</sup> In most of the previous studies, a Si capping layer was formed on a Ge substrate either by epitaxial growth of several monolayers of Si or by annealing in ambient  $SiH_4$  (or  $Si_2H_4$ ).<sup>21–24</sup> However, not many studies of Si-containing passivation layers grown by an atomic layer deposition (ALD) method on Ge substrates have been reported.

Houssa et al. simulated the atomic configurations of the interface between various rare-earth oxide materials and Ge with first-principles calculations.<sup>25</sup> The results revealed the feasibility of La<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> as an effective passivation layer on Ge to suppress the formation of dangling bonds other than HfO<sub>2</sub>. Kato et al. reported that an Al<sub>2</sub>O<sub>3</sub> inter layer effectively suppressed the formation of a Ge oxide interlayer in a lanthanum (La) oxide/Al<sub>2</sub>O<sub>3</sub>/Ge gate stack structure. The formation of  $\text{GeO}_x$  (x < 2) was suppressed by increasing the thickness of the  $Al_2O_3$  interfacial layer up to 1 nm.<sup>26</sup> In contrast, the adoption of a capping layer, which could suppress the volatilization of GeO from the GeO<sub>2</sub> surface, and, thus, the accompanying interfacial reaction, has not been studied in detail compared with the interfacial passivation layer approach. Jung et al. studied various interfacial passivation layers between HfO<sub>2</sub> thin films and Ge substrates to improve the charge trapping properties and the C-V hysteresis characteristics. The  $SiO_xN_y$  interfacial passivation layer reduced both the C-V hysteresis and the charge trapping properties. The chemical analysis revealed that the SiO<sub>x</sub>N<sub>y</sub> passivation interface layer was effective in suppressing the inter mixing between the HfO<sub>2</sub> film and the Ge substrate and the formation of Ge suboxides at the interface.2

In this study, ALD of ultrathin Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> layers was adopted as interfacial passivation and capping layers, respectively, with lanthanum-silicate (La-silicate) films on Ge substrates. ALD of the La-silicate films was carried out by sequential injections of the Si containing tris[bis- $(trimethylsilyl)amino]lanthanum (La[N{Si(CH_3)_3}_2]_3) and$ ozone  $(O_3)$  as the La-precursor and the oxygen source, respectively. ALD is the most feasible and competitive process for fabricating high-quality gate dielectric thin films with conformal deposition and high accuracy in the film thicknesses, making it compatible with semiconductor fabrication technologies that are suitable for mass production. During deposition of the La-silicate films, SiH<sub>2</sub>(NC<sub>2</sub>H<sub>5</sub>CH<sub>3</sub>)<sub>2</sub> (BEMAS) and SiH<sub>2</sub>(N( $C_2H_5$ )<sub>2</sub>)<sub>2</sub>(BDEAS) were additionally injected to control the Si concentrations ([Si]/([Si]+[La])) in the high-k films, as well as the accompanying electrical properties. Ultrathin interfacial Al<sub>2</sub>O<sub>3</sub> layers whose thicknesses were controlled by deposition cycles (2, 3, 5, and 10 cycles) were formed between the La-silicate film and the Ge substrate by ALD. Additionally, ALD SiO<sub>2</sub> was chosen as the material for

the capping layer on the La-silicate films. The multistack of the  $Al_2O_3$  passivation, high-k La-silicate, and capping SiO<sub>2</sub> layers effectively decreased the C–V hysteresis down to 100 mV. This is one of the best results reported to date for a MOS capacitor adopting a Ge substrate. It has to be noted that the primary goal of this work was to elucidate the role of interfacial barrier and capping layers in suppressing the deleterious effects originating from the chemical interactions between the high-k film and Ge substrate. Therefore, relatively thick dielectric films (6–7 nm) were adopted which efficiently suppress other effects that may come from the leakage current and charge trapping.

## **II. EXPERIMENT PROCEDURE**

La-silicate films were grown on a cyclic HF-cleaned Ga-doped p-type (100) Ge substrate at a wafer temperature of 310 °C in a travelingwave-type 4-inch-diameter scale thermal ALD reactor with a liquid delivery system using  $La[N{Si(CH_3)_3}_2]_3$  dissolved in hexane (0.15 mol/L) as the La precursor. Various passivation interfacial layers and capping layers, such as Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, and La<sub>2</sub>O<sub>3</sub>, were also deposited by ALD. Al(CH<sub>3</sub>)<sub>3</sub>(TMA), BEMAS, BDEAS, and (tris(isopropylcyclopentadienyl)lanthanum) (La('PrCp)3) were used as the metal precursors for Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, and La<sub>2</sub>O<sub>3</sub>, respectively. O<sub>3</sub> with a concentration of 110 g/Nm<sup>3</sup> was used as the oxygen source for the Lasilicate, Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, and La<sub>2</sub>O<sub>3</sub> films. La[N{Si(CH<sub>3</sub>)<sub>3</sub>}<sub>2</sub>]<sub>3</sub>was vaporized at 190 °C and delivered to the reactor with help from an Ar carrier gas of 200 standard cubic centimeter per minute (sccm). The injection time for the La[N{Si(CH<sub>3</sub>)<sub>3</sub>}<sub>2</sub>]<sub>3</sub> precursor solution was controlled in milliseconds to precisely deliver it to the vaporizer. The precursor injection time for the La-silicate,  $\mathrm{La}_2\mathrm{O}_3,\,\mathrm{SiO}_2,\,\mathrm{and}\,\,\mathrm{Al}_2\mathrm{O}_3$ sources and the O3 were fixed at 0.1 ms and 10, 1, 1, and 5 s, respectively. Under these conditions, the growth rates of the Lasilicate, La<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub> films were 0.08, 0.085, 0.09, and 0.1 nm/cycle, respectively. Under these conditions, the growth of the 1nm-thick La-silicate and  $SiO_2$  films required 416 and 188 s, respectively. To control the Si concentration in the La-silicate films, a Si precursor was injected alternately during the La silicate film deposition. The thickness of the Al<sub>2</sub>O<sub>3</sub> passivation layer was controlled by the deposition cycles, from two cycles to 10 cycles ( $\sim$ 1 nm), and the SiO<sub>2</sub> capping layer was fixed at 2 nm. The base pressure of the ALD chamber was maintained below 0.01 Torr, and the operational pressure was ~0.3 Torr. The film thicknesses were measured with an ellipsometer (ESM-300; J.A. Woollam Co., Inc.) and X-ray reflectivity (PANalytical; X'Pert PRO MPD) and were confirmed by highresolution transmission electron microscopy (HRTEM; JEOL, JRM 2100F). The depth profiles of the elements in the films were examined by Auger electron spectroscopy (AES; PerkinElmer 660). The chemical states and electronic structures of the films were analyzed by X-ray photoelectron spectroscopy (XPS; Sigma Probe) using monochromatic Al K $\alpha$  as the X-ray source. All of the examined samples did not undergo post-deposition annealing after the film growth, and forming gas annealing was not carried out after deposition of the top electrode. This was performed so that no intermixing between the deposited layers was induced, allowing for clear identification of the role of the different layers and the film compositions on the chemical structure and accompanying electrical properties. Therefore, it is anticipated that appropriate annealing of the films before and after deposition of the electrode could further improve the electrical performance, although the optimized sample structures reported in this work already exhibited an impressive electrical performance without any thermal treatment. This examination is on-going and will be reported elsewhere.

For MOS capacitor fabrication, Pt top electrodes were deposited by electron-beam evaporation using a shadow mask. C–V curves, constant-voltage stress (CVS), and the interface state density  $(D_{\rm it})$  were evaluated with a conductance method, and the leakage current density-voltage (J<sub>g</sub>-V) characteristics were measured using a HP 4284 LCR meter and a HP 4140B picoammeter/DC voltage source, respectively. The capacitance equivalent thickness (CET) was

calculated from the accumulation capacitances measured at 1 MHz, taking quantum mechanical effects into consideration. A voltage was applied to the Pt top electrode, while the Ge substrate was grounded via an In contact.

## **III. RESULTS**

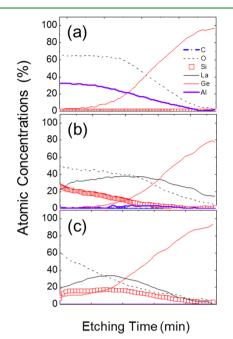

III-1. Effects of the Si-Concentration in La-Based Oxide Films. The structure and electrical properties of single layer La-silicate films were examined for different Si concentrations. In this set of experiments, the La<sub>2</sub>O<sub>3</sub> films were deposited using La(<sup>i</sup>PrCp)<sub>3</sub> as the precursor. The La-silicate films were deposited using La[N{Si(CH<sub>3</sub>)<sub>3</sub>}<sub>2</sub>]<sub>3</sub>, and the Si-concentration controlled La-silicate films were deposited by alternative injections of La[N{Si(CH<sub>3</sub>)<sub>3</sub>}<sub>2</sub>]<sub>3</sub> and either BEMAS or BDEAS precursors. The Si concentrations in the asdeposited La-silicate films using only La[N{Si(CH<sub>3</sub>)<sub>3</sub>}<sub>2</sub>]<sub>3</sub> as the precursor were ~25%, which was confirmed with an Auger depth profile, as shown in Figure 1b. The Si concentrations

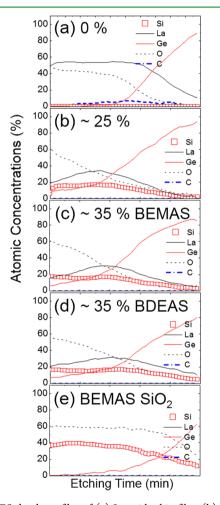

Figure 1. AES depth profiles of (a) La-oxide thin film, (b) La-silicate thin film, Si concentrations controlled La-silicate film by (c) BEMAS-Si precursor, (d) BDEAS-Si precursor, and (e)  $SiO_2$  thin film by BEMAS precursor.

were obtained using the average concentrations of La and Si through the oxide layer in the AES results. Figure 1a showed that the Si concentrations for the pure  $La_2O_3$  thin films deposited using  $La(^{i}PrCp)_3$  as the precursor were below the detection limit of the AES (< ~1%). The concentration of Ge in the  $La_2O_3$  films was also minimized under this condition.

The ALD cycle ratio of the SiO<sub>2</sub> and La silicate was controlled to make the Si concentration in the La-silicate films ~35% (Figure 1c and d, where BEMAS and BDEAS were adopted, respectively). The Ge-concentration in the La-silicate film was significantly observed up to the film surface. Figure 1e shows the AES depth profile of an ALD SiO<sub>2</sub> film using BEMAS as the precursor, which revealed that the Ge concentration was not negligible, especially near the interface, but it was negligible near the film surface. From the AES results in Figure 1, the Ge concentration in the La-silicate film was much higher than in the non-doped La2O3 and SiO2 films, while the Ge concentration was almost independent of the Si concentration under the experimental conditions used. To understand the influence of the chemical changes in the films, C-V measurements were performed for a given oxide film (physical) thickness of  $\sim 6$  nm, which included the thickness of the interfacial layer. The C-V hysteresis and CET values were examined from the C-V curves when the gate voltage was swept from the depletion region (positive voltage) to the accumulation region (negative voltage) and back to the depletion region. The C-V hysteresis was extracted from the flat band voltage difference in the two C–V curves during the forward and reverse sweeps. Figure 2 shows the variations in

**Figure 2.** C–V hysteresis and CET as a function of Si concentrations of La-based oxide films.

the C–V hysteresis voltage (left hand ordinate, closed symbols) and the CET (right hand ordinate, open symbols) of the oxide films as a function of the Si concentration. The CET increased slightly with an increasing Si concentration in the La-silicate films because of the decreased k value of the oxide layer, while the hysteresis voltage decreased rapidly with an increasing Si concentration. These tendencies were not dependent on the type of Si precursor used for the La-silicate film growth. When the high-k films were deposited directly onto the HF cleaned Ge substrates, a significantly large C-V hysteresis of ~1000 mV was observed, suggesting that a high density of electrically active defects was created near the interface or inside the bulk high-k film, which is consistent with a previous report.<sup>18</sup> This suggests that the non-doped film underwent a severe interfacial reaction, resulting in a higher trap density either near the interface or inside the bulk film. Incorporation of Ge into the high-k film could be induced in two ways; one was the solidstate diffusion of Ge atoms (or ions) from the Ge substrate to

the film, and the other was the trapping of GeO, which was produced by the desorption reaction (GeO<sub>2</sub> + Ge  $\rightarrow$  2GeO) at the interface with the Ge-substrate and volatilization of the GeO. Some of the volatilized GeO was trapped in the film during ALD of the high-k films. More details on this aspect of Ge-incorporation are presented in the Discussion section. Among the two mechanisms, the latter is believed to be largely responsible for the Ge-incorporation in the high-k films because there is no obvious reason for how the La2O3 film could sufficiently suppress the solid-state diffusion of Ge. The almost negligible Ge concentration in the La2O3 film therefore suggests that the La<sub>2</sub>O<sub>3</sub> layer cannot prevent volatilization of the GeO that was produced by the desorption reaction at the interface, which could cause the high interfacial defect density. In contrast, when the Si concentration of the La-silicate film was increased from 0% to  $\sim$ 35%, the C-V hysteresis was decreased by  $\sim 40\%$  and the hysteresis voltage became  $\sim 600$ mV when the Si concentration was ~35%. The relatively high Ge concentration in the film suggested that the volatilization of GeO from the film surface was suppressed, inducing fewer interfacial reactions with the Ge substrate.

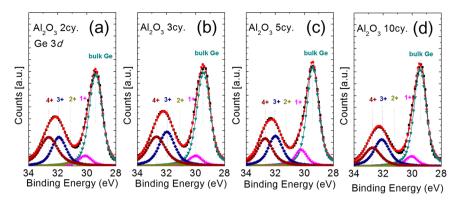

To achieve a better understanding of this behavior, the chemical bonding states of various La-silicate films on Ge substrates were examined by XPS. The degree of formation of the Ge oxides was focused on with XPS. Figure 3a shows the

Figure 3. Ge 3d core level of (a) various Si concentration of La-based oxide film using BEMAS precursor, the explicit deconvolution for Geoxide for (b) pure La-silicate film and (c) ~30 % and (d) ~35 % Si concentrations controlled La-silicate films using BEMAS precursor, and (e) ~30 % and (f) ~35 % Si concentrations controlled La-silicate films using BDEAS precursor.

Ge 3d spectra of pure-La<sub>2</sub>O<sub>3</sub> and La-silicate films with Si concentrations of ~25%, 30%, and 35%, where BEMAS was adopted as the Si precursor. The energy scale was calibrated by fixing the Ge 3d peak of the bulk Ge (Ge<sup>0</sup>) at a binding energy (BE) of 29.4 eV, which was clearly observed because the thickness of the high-*k* films was thin enough such that it did not greatly attenuate the photoelectrons generated from the

Ge-substrates. This also suggested that the BE-shifted Ge 3d signal originated not only from the oxide layer but also from the interfacial layer. A clear peak at a BE higher than that of bulk Ge was observed, and the BE shifts of the Ge-oxide peak from the Ge<sup>0</sup> were 2.91, 3.12, 3.27, and 3.43 eV for La<sub>2</sub>O<sub>3</sub> for La silicates with Si concentrations of 25%, 30%, and 35%.

The lack of a Ge signal in the La2O3 layer in Figure 1a revealed that the oxidized Ge 3d peak in the XPS mainly originated from the Ge-oxide layer located at the interface between the La2O2 film and Ge substrate. To understand the variations in the chemical states of the films with different Si concentrations, the Ge 3d peaks were deconvoluted, assuming the presence of five Ge oxidation states (Ge<sup>0</sup>, Ge<sup>1+</sup>, Ge<sup>2+</sup>, Ge<sup>3+</sup>, and  $Ge^{4+}$ ), the spectra related to the Ge oxide could be deconvoluted into four Ge oxide peaks (Ge1+, Ge2+, Ge3+, and Ge<sup>4+</sup> with BE shifts from the bulk Ge 3d of 0.8, 1.8, 2.6, and 3.4 eV, respectively<sup>28,29</sup>). These results are included in Figure 3b-f. After subtracting the background intensities, the area of each peak was calculated, and the (Ge<sup>4+</sup> peak)/(sum of Ge<sup>1+</sup>, Ge<sup>2+</sup>, and Ge3+ peaks) ratios were found. Figure 3b-f show the variations in the ratio as a function of the Si concentration in the La2O3 and La-silicate films. Figure 3 also includes the corresponding results achieved with the La-silicate films that adopted BDEAS. The ratios were almost independent of the type of Si precursor used, but they were largely determined by the Si concentration and increased with an increasing Si concentration. The generation of Ge suboxides is considered to contribute to the large hysteresis voltage in the C-V curves as well as the fast interface trap states  $(D_{it})$ , even at the cost of increasing the CET.<sup>10</sup> These results suggest that higher Si concentrations in the La-silicate films suppressed the Ge suboxide formation at the Ge interface, which was effective in decreasing the C–V hysteresis voltage.

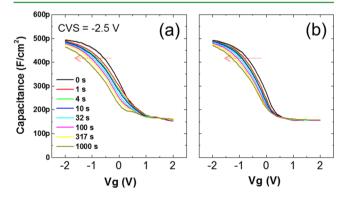

Figure 4 shows variations in the C–V curves with different stress times for CVS tests (with a gate stress voltage of -2.5 V)

**Figure 4.** C–V curves for CVS (with a gate stress voltage of -2.5 V) on MOSCAPs with the structures of (a) Pt/La-oxide/*p*-Ge and (b) Pt/La-silicate (~25 % Si concentration)/*p*-Ge.

on MOS capacitors with structures of (a) Pt/La<sub>2</sub>O<sub>3</sub>/p-Ge and (b) Pt/La-silicate (Si concentration of ~25%)/p-Ge. The C–V curves were recorded for fresh samples under forward and reverse bias sweeps with a gate voltage sweep rate of 50 mVs<sup>-1</sup> and after eight successive stress cycles (0, 1, 4, 10, 32, 100, 317, and 1000 s). The flat-band voltage shift ( $\Delta V_{\rm FB}$ ), which is related to the fixed charge trapping in the devices, and the slope change of the C–V curve, which is related to the generation of  $D_{iv}$  were determined from the figure. The La-oxide film had a large  $\Delta V_{\rm FB}$  in the negative voltage direction as well as changes

in the slopes of the C–V curves, while the La-silicate film had a notable change in the slopes of the C–V curves. This suggests that the deterioration of the bulk properties in the La<sub>2</sub>O<sub>3</sub> films (fixed charge generation) was higher than in the La-silicate films, while the degradation of the interfacial trap properties was similar. The La-oxide film had a larger C–V hysteresis than the La-silicate film. This was mainly caused by a larger number of trapped charges in the bulk, and the contribution of the interface trap density could be similar to that of La silicate. The XPS and CVS results suggested that the higher Si concentration in the La-silicate films suppressed the formation of Ge suboxides at the Ge interface and bulk traps in the films, which was effective in decreasing the C–V hysteresis.

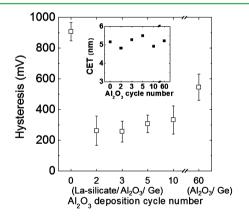

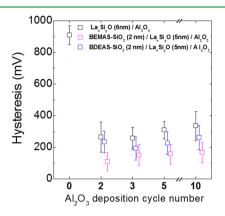

III-2. Adoption of an  $Al_2O_3$  Interface Passivation Layer. To further improve the quality of the interface, and thus decrease the C–V hysteresis, a thin  $Al_2O_3$  layer was inserted between the La-silicate film (25% Si concentration) and the Ge substrate. In this experiment, no additional Siprecursor injection was performed during the high-*k* film growth. The thickness of the  $Al_2O_3$  layer was varied by changing the deposition cycles from 2 to 10 cycles, with 10 deposition cycles being coincident with a ~1-nm-thick  $Al_2O_3$ film. MOS capacitors (MOSCAPs) with ~6-nm-thick Lasilicate films with a thin  $Al_2O_3$  passivation layer were fabricated. The C–V curve shifted toward the positive voltage direction with an increasing number of  $Al_2O_3$  deposition cycles, because there were negative fixed charges in the  $Al_2O_3$  films.<sup>30,31</sup> Figure 5 shows the variations in the C–V hysteresis voltages for the

Figure 5. C–V hysteresis of La-silicate MOSCAPs with an ultrathin  $Al_2O_3$  passivation interface layer as a function of  $Al_2O_3$  deposition cycles. Inset figure shows CET changes as a function of  $Al_2O_3$  deposition cycles.

La-silicate films as a function of the number of  $Al_2O_3$  deposition cycles and  $Al_2O_3$  films (60 cycles ~6 nm). The data without an  $Al_2O_3$  cycle were taken from Figure 2. When there were two and three  $Al_2O_3$  deposition cycles, a passivation interface layer was inserted between the La-silicate and the Ge substrate, and the C–V hysteresis had its lowest value (~250 mV). Further increasing the number of  $Al_2O_3$  cycles increased the value to ~350 mV when 10 cycles were adopted. The C–V hysteresis of a ~6-nm-thick  $Al_2O_3$  layer was ~550 mV, suggesting that the appropriate combination of the La-silicate layer and the interfacial passivation  $Al_2O_3$  layer (2–3 cycles) was required to decrease the C–V hysteresis. Inset figure shows the CET values of the various samples in Figure 5. There were variations in the CET values for the different samples, but the degree of variation (~0.5 nm) was not large.

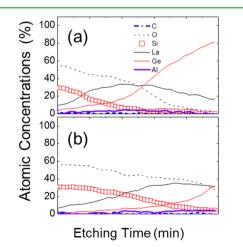

Figure 6a–c show the AES depth profiles, 6.0 nm in thickness, for  $Al_2O_3$ , La-silicate with  $Al_2O_3$  (with two cycles),

Figure 6. AES depth profiles of (a)  $Al_2O_3/p$ -Ge, (b) La-silicate/ $Al_2O_3$  (2 cycles)/p-Ge, and (c) La-silicate/p-Ge.

and La-silicate films, respectively. The  $Al_2O_3$  film had almost no impurities in the bulk film, proving its effective barrier properties against GeO volatilization and Ge diffusion, but there could also be an interfacial reaction. This can be understood from the tailed Ge distribution near the interface. The adoption of  $Al_2O_3$  cycles, even though the  $Al_2O_3$  layer was ultrathin, decreased the Ge concentration within the La-silicate film, and the density of defect centers related to Ge in the Lasilicate film was decreased.

The chemical states in the films were further examined with XPS. The Ge 3d peaks and the deconvoluted results for Lasilicate films with the different Al<sub>2</sub>O<sub>3</sub> cycles are shown in Figure 7. The films generally showed oxidized Ge 3d peaks. The ratios of (Ge<sup>4+</sup> peak)/(sum of Ge<sup>1+</sup>, Ge<sup>2+</sup>, and Ge<sup>3+</sup> peaks) were calculated using the same method as in Figure 3b-d for different Si concentrations in the La-silicate films. The values for 2, 3, 5, and 10 Al<sub>2</sub>O<sub>3</sub> cycles were 46%, 42%, 39%, and 35%, respectively. In Figure 3b, the ratio for the La-silicate film with a Si concentration of 25% was ~40%. It increased to 46% in Figure 7 when only two Al<sub>2</sub>O<sub>3</sub> cycles were adopted before the La-silicate film was deposited. Therefore, the improvement in the C-V hysteresis (shown in Figure 5) can be understood because less Ge was incorporated into the bulk of the La-silicate films and there was lesser of defective Ge-oxide at the interface. However, a further increase in the number of Al<sub>2</sub>O<sub>3</sub> cycles decreased the ratio, suggesting that there was an increase in the formation of Ge suboxides, which is consistent with the degraded C-V hysteresis performance shown in Figure 5.

Hinkle et al. and Milojevic et al. reported that the thickness of the native oxide formed on GaAs and Ge substrates decreased after  $Al_2O_3$  was deposited by the ALD method using TMA and  $H_2O$ .<sup>32,33</sup> These reports suggested that the decrease in the thickness of the oxide inter layers was caused by the strong reduction of the TMA precursor.<sup>32,33</sup> It is believed that

Figure 7. Ge 3d core level for the explicit deconvolution for Ge-oxide (a) La-Silicate/Al<sub>2</sub>O<sub>3</sub> (two cycles)/*p*-Ge, (b) La-silicate/Al<sub>2</sub>O<sub>3</sub> (three cycles)// *p*-Ge, (c) La-silicate/Al<sub>2</sub>O<sub>3</sub> (five cycles)/*p*-Ge, and (d) La-silicate/Al<sub>2</sub>O<sub>3</sub> (10 cycles)/*p*-Ge.

the same interfacial cleaning effect occurred for the optimum number of  $Al_2O_3$  cycles (two to three cycles), while further increasing the number of  $Al_2O_3$  cycles (more than five cycles) deteriorated the interfacial properties with the formation of the sub-oxides.

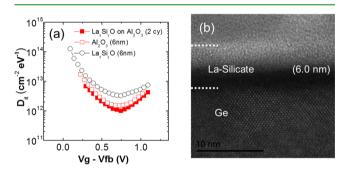

To further study the interfacial properties of the La-silicate films, the  $Al_2O_3$  passivation (two cycles) interface with La-silicate, and  $Al_2O_3$  films, the  $D_{it}$  was extracted using a conductance method. Figure 8a shows the  $D_{it}$  of the three

Figure 8. (a) Interface state density vs.  $V_g - V_{FB}$  of Al<sub>2</sub>O<sub>3</sub>/Ge, Lasilicate/Al<sub>2</sub>O<sub>3</sub> (two cycles)/Ge, and Lasilicate/Ge and (b) TEM images for Lasilicate/Ge.

samples as a function of the gate voltage-flat band voltage ( $V_g - V_{FB}$ ). Al<sub>2</sub>O<sub>3</sub> passivation of the La-silicate films had the smallest  $D_{it}$  among the films studied, suggesting that the ultrathin Al<sub>2</sub>O<sub>3</sub> passivation film effectively reduced the interfacial state density. Figure 8b shows a cross-sectional TEM image of the La-silicate film, confirming the thickness was ~6 nm and the film

maintained an amorphous structure. The two films also had a similar thickness and structure (TEM images not shown).

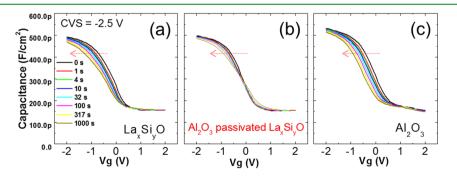

CVS tests with a  $V_g$  of -2.5 V were performed on the three samples. Figure 9 shows the results for (a) Pt/La-silicate/p-Ge, (b) Pt/La-silicate with an Al<sub>2</sub>O<sub>3</sub> passivation layer (two deposition cycles)/p-Ge, and (c) Pt/Al<sub>2</sub>O<sub>3</sub>/p-Ge. While the single-layer La-silicate and the  $Al_2O_3$  film showed  $D_{it}$ degradation (decreasing slope in the C–V curves) and positive charge trapping (parallel shift in the C-V curve in the negative direction), the La-silicate film with an Al<sub>2</sub>O<sub>3</sub> passivation layer with two cycles showed improved reliability characteristics; it did not show any notable changes in the  $V_{\rm FB}$ , whereas degradation in the D<sub>it</sub> was still persistent. This result indicated that the Al<sub>2</sub>O<sub>3</sub> film had a large bulk trap density, which induced the large C-V hysteresis, irrespective of the interfacial properties with the Ge substrate. The C-V hysteresis was governed by both the interfacial properties with the Ge substrate and the oxide bulk trap density. These variations in the chemical composition and structure at the interface and in the bulk film, and the accompanying electrical performance, must be closely related to the formation of GeO and its volatilization from the interface or the bulk film. Once volatilization occurred, identifying the GeO formation became difficult via chemical analyses such as AES and XPS. Therefore, capping of the La-silicate film with a thin SiO<sub>2</sub> layer was performed. The SiO<sub>2</sub> capping layer also largely improved the electrical properties.

III-3. Multistacked La-Silicate Films with an  $Al_2O_3$ Passivation Layer and a SiO<sub>2</sub> Capping Layer. A SiO<sub>2</sub> layer with a thickness of 2 nm was deposited on the 5 nm-thick La-silicate films (25% Si concentration) with different  $Al_2O_3$ passivation layer cycles (2–10 cycles) using BEMAS or BDEAS

Figure 9. C–V curves of CVS on MOSCAPs with the structures of (a) Pt/La-silicate/Ge, (b) Pt/La-silicate/Al<sub>2</sub>O<sub>3</sub> (two cycles)/Ge, and (c) Pt/Al<sub>2</sub>O<sub>3</sub>/Ge.

Si precursors to examine the effects of capping the high-k film with a thin SiO<sub>2</sub> layer. Figure 10 shows the variations in the C–

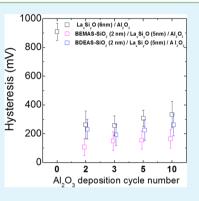

Figure 10. C–V hysteresis of La-silicate MOSCAPs with BEMAS and BDEAS  $SiO_2$  capped La-silicate with  $Al_2O_3$  interface passivation layer on Ge as a function of  $Al_2O_3$  deposition cycles.

V hysteresis for the three sets of samples as a function of the number of Al<sub>2</sub>O<sub>3</sub> ALD cycles: La-silicate with only an Al<sub>2</sub>O<sub>3</sub> passivation layer and two different types of SiO<sub>2</sub> capping layer with Al<sub>2</sub>O<sub>3</sub> passivated La-silicates. The data for La-silicate with only an Al<sub>2</sub>O<sub>3</sub> passivation layer were reproduced from Figure 5 for a comparison. The SiO<sub>2</sub> capping layer was generally an effective method in decreasing the C-V hysteresis voltage. Adoption of the BEMAS Si-precursor was especially effective in decreasing the C-V hysteresis, and a minimum value of ~100 mV was observed with the optimum number of Al<sub>2</sub>O<sub>3</sub> cycles of two. Among the many samples tested under this condition to obtain statistically meaningful data, one sample showed a hysteresis voltage as small as 50 mV. Therefore, SiO<sub>2</sub> capping in combination with Al<sub>2</sub>O<sub>3</sub> passivation with the optimum number of cycles is a promising method in decreasing the C-V hysteresis in the high-k gate stack films on Ge substrates.

Figure 11 shows AES depth profiles for (a) BEMAS and (b) BDEAS  $SiO_2$ -capped La-silicate layers with an  $Al_2O_3$  (two cycles) interface passivation layer on Ge. The compositions of the deposited films were almost identical for both  $SiO_2$  capping layers. The presence of the thin  $SiO_2$  capping layer caused the Si concentration in the La-silicate to appear to be higher than

Figure 11. AES depth profiles for (a) BEMAS and (b) BDEAS  $SiO_2$  capped La-silicate with  $Al_2O_3$  (two cycles) interface passivation layer on Ge.

that with no SiO<sub>2</sub> capping layer, which is believed to be a result of the limited depth resolution of the AES system. A comparison between the AES depth profiles with the data for the samples with no  $SiO_2$  capping layer (Figure 6b and c) showed that the Ge concentration in the SiO<sub>2</sub>-capped Lasilicate film was higher, which is almost comparable to the Lasilicate films with no capping layer and an Al<sub>2</sub>O<sub>3</sub> passivation layer shown in Figure 1b-d. This was unexpected since the adoption of an Al<sub>2</sub>O<sub>3</sub> passivation layer suppressed the Geconcentration in the La-silicate films (Figure 6), and the SiO<sub>2</sub> layer did not induce high Ge concentrations in the SiO<sub>2</sub> films either (Figure 1e). Considering the processing conditions for the sequential deposition of ultrathin Al<sub>2</sub>O<sub>3</sub>/5-nm-thick and Lasilicate/2-nm-thick  $SiO_2$ , the Ge concentration in the high-k film must have been low when the ultrathin Al<sub>2</sub>O<sub>3</sub>/5-nm-thick La-silicate films were deposited. Therefore, the higher Ge concentration must have been induced during the final SiO<sub>2</sub> deposition step. This aspect is discussed in detail in the Discussion section.

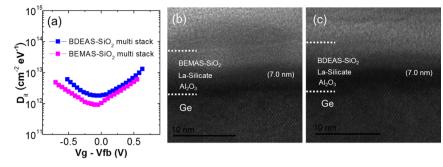

Figure 12a shows the  $D_{it}$ 's for BEMAS and BDEAS SiO<sub>2</sub>capped La-silicate layers with an Al<sub>2</sub>O<sub>3</sub> interface passivation layer as a function of the  $V_{g}-V_{FB}$ . BEMAS-SiO<sub>2</sub>-capped Lasilicate with an Al<sub>2</sub>O<sub>3</sub> interface passivation layer had a lower  $D_{it}$ than the BDEAS-SiO<sub>2</sub>-capped sample. A minimum  $D_{it}$  of less than 10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup> was achieved for the best condition. Figure 12b and c show cross-sectional HRTEM images for the BEMAS- and BDEAS-SiO<sub>2</sub>-capped La-silicate with an Al<sub>2</sub>O<sub>3</sub> (two cycles) interface passivation layer on Ge. Although the detailed film structure was difficult to see because of the inappropriate TEM sample quality, the total thickness of ~7 nm, which was expected from the thickness of the La-silicate (5 nm) and SiO<sub>2</sub> (2 nm) films, could be estimated for both cases.

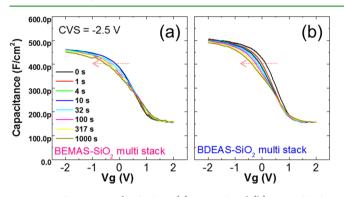

The C–V curves for the CVS tests on Pt/BEMAS SiO<sub>2</sub> 2 nm/La-silicate 5 nm/Al<sub>2</sub>O<sub>3</sub> (two cycles)/*p*-Ge and Pt/BDEAS SiO<sub>2</sub> 2 nm/La-silicate 5 nm/Al<sub>2</sub>O<sub>3</sub> (two cycles)/*p*-Ge are shown in Figure 13a and b, respectively. The BEMAS-SiO<sub>2</sub>-capped multistack layer had small changes in the slopes of the C–V curves, suggesting that degradation of the  $D_{\rm it}$  was minimized in this sample, while that in the BDEAS-SiO<sub>2</sub>-capped sample had a slightly more severe change in the slope. The C–V hysteresis after CVS tests for 1000 s for the BEMAS-SiO<sub>2</sub>-capped sample remained identical to the V<sub>FB</sub> shift of the initial position, suggesting that the sample was robust against electrical stress.

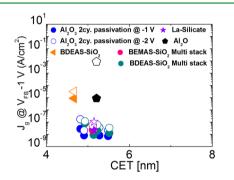

Figure 14 shows a summary of the leakage current  $(J_{gr})$  measured at  $V_{\rm FB} - 1$  V) vs the CET for the samples discussed in this work. Because of the generally high physical thickness and the accompanying CET, this did not have significant importance in estimating the dielectric performance of the samples. However, it can be confirmed that the multistack sample with a BEMAS SiO<sub>2</sub> capping layer showed a stable leakage current at a CET of 5 nm, which is not necessarily the case for the Al<sub>2</sub>O<sub>3</sub> or BDEAS-SiO<sub>2</sub>-capped samples.

## **VI. DISCUSSIONS**

The Ge impurities in the high-*k* dielectric films with various oxidized forms acted as the defect centers, which deteriorated the electrical performance. However, as mentioned in the previous section, the incorporation of Ge into the high-*k* film appeared to originate not from the solid-state diffusion from the Ge substrate but from the trapping of volatile GeO during the ALD process. This is different from the Si substrate where Si diffusion almost always occurred during high-*k* film growth or

Figure 12. Interface state density vs.  $V_g - V_{FB}$  for (a) BEMAS and BDEAS SiO<sub>2</sub> capped La-silicate with Al<sub>2</sub>O<sub>3</sub> (two cycles) interface passivation layer on Ge. TEM images for (b) BEMAS and (c) BDEAS SiO<sub>2</sub> capped La-silicate Al<sub>2</sub>O<sub>3</sub> (two cycles) interface passivation layer on Ge.

Figure 13. C–V curves for CVS on (a) BEMAS and (b) BDEAS  $SiO_2$  capped La-silicate with  $Al_2O_3$  (two cycles) interface passivation layer on Ge.

**Figure 14.** Insulating properties for various high-*k* thin films deposited with thermal ALD.

post-deposition annealing.<sup>34</sup> The significant Si diffusion was mainly ascribed to the higher oxide formation energy of SiO<sub>2</sub> compared with that of GeO<sub>2</sub>. Thus, the driving force for the Si diffusion was not just the concentration gradient of Si but the tendency to form SiO<sub>2</sub>. It has been observed that an ultrathin SiO<sub>2</sub> layer was formed, even on high-*k* HfO<sub>2</sub> film surfaces, after post-deposition annealing by the diffusion of Si from the Si substrate to the film surface, where it oxidized.<sup>34</sup> This was also the main reason why an interfacial reaction for the formation of volatile SiO (SiO<sub>2</sub> + Si  $\rightarrow$  2SiO) was highly unlikely.

The key to suppressing the incorporation of Ge atoms (or ions) into the high-k film was to suppress the desorption reaction between GeO<sub>2</sub> and Ge. During ALD of high-k oxides, the highly reactive O<sub>3</sub> was adopted as the oxygen source, and the thermodynamic and kinetic environments for this reaction were quite complicated. It is believed that the desorption reaction is in competition with the GeO<sub>2</sub> formation reaction by the strong oxidation power of O<sub>3</sub>. In addition, there must always be a native oxide, which is vulnerable to inducing the desorption reaction. Therefore, to correctly interpret the experimental results in section III, understanding these complicated reactions is necessary. Unfortunately, this is generally not easy because once GeO becomes volatile, it cannot be traced by any chemical analysis tools, such as AES or XPS. The pure La<sub>2</sub>O<sub>3</sub> film shown in section III-1 serves as a representative example for this difficulty; the film did not contain any notable Ge impurities, but the electrical performance was the lowest among the samples tested. This must have been caused by the low blocking performance of the pure La<sub>2</sub>O<sub>3</sub> film to the volatilization of GeO that was produced at the high-k/Ge interface during ALD of the La<sub>2</sub>O<sub>3</sub> film. As the GeO can be easily removed from the interface through the  $La_2O_3$  film, the desorption reaction (GeO<sub>2</sub> + Ge  $\rightarrow$  2GeO) kept occurring and the interface and the high-k film bulk deteriorated. In contrast, the La-silicate films had more efficient properties of blocking the GeO diffusion through them, so they could contain a substantial amount of Ge (or  $GeO_x$ ). Under this circumstance, the partial pressure of GeO at the interface must be higher than that for the La<sub>2</sub>O<sub>3</sub> film, so that the progression rate of the desorption reaction can be retarded, inducing an improved electrical performance. By the extension of this consideration on the desorption reaction, the results from the Al<sub>2</sub>O<sub>3</sub> passivation and SiO<sub>2</sub> capping can be understood.

When the Al<sub>2</sub>O<sub>3</sub> passivation layer is considered, however, another complication becomes involved as the high reactivity of TMA can remove the native GeO<sub>2</sub> by reduction. The almost negligible Ge concentration in the La-silicate film when two to three Al<sub>2</sub>O<sub>3</sub> passivation ALD cycles were adopted suggests that the native GeO<sub>2</sub> was effectively removed and that the desorption reaction that originated from the native  $GeO_2$ layer could be largely suppressed. This in turn suggests that the incorporated Ge in the La-silicate films (shown in Figure 1b-d) mainly originated from the desorption reaction of the native GeO<sub>2</sub>. The higher  $Ge^{4+}$  content (46%) in the XPS with two Al<sub>2</sub>O<sub>3</sub> passivation cycles compared with the no passivation case (40%) revealed that the ALD process using TMA and O<sub>3</sub> preferred oxidation of the Ge surface to GeO<sub>2</sub> compared with the progression of the desorption reaction, which is a reasonable consequence of the exposure of the cleaned Ge surface (by TMA) to O3. The increased Al2O3 ALD cycles decreased the Ge4+ content, which could be understood because the oxidation of Ge to  ${\rm GeO}_2$  was retarded by the increased Al<sub>2</sub>O<sub>3</sub> thickness, while the desorption reaction started to increase.

When the 2-nm-thick  $SiO_2$  capping layer was adopted on the 5-nm-thick La-silicate/(two cycles)  $Al_2O_3$  passivated films, the

Ge concentration in the film increased (Figure 11). According to the data shown in Figure 6b and the related discussions above, the 5-nm-thick La-silicate/(2 cycles) Al<sub>2</sub>O<sub>3</sub>passivated films had a negligible Ge concentration and the increased Ge concentration was induced by the additional SiO<sub>2</sub> capping process. When compared with the ALD processing time of 6nm-thick La-silicate film in Figure 6, the 5-nm-thick La-silicate film required a 416 s shorter processing time, and the additional 2-nm-thick SiO<sub>2</sub> film required an ALD processing time of 375 s. Therefore, the increased Ge concentration in the film was not caused by the overall increase in the ALD processing time. As described previously, the two-cycle Al<sub>2</sub>O<sub>3</sub> passivation process may have already removed the native  $GeO_2$ . The only possible source of GeO (the Ge contents in the La-silicate film) must have originated from the reaction between the oxidized GeO<sub>2</sub> (by the  $O_3$  in ALD process) and the Ge substrate. As this was far less active than the desorption reaction between the native GeO<sub>2</sub> and Ge, the amount of GeO produced was quite small. This small amount might have volatilized through the La silicate, even though it possessed certain barrier properties over the GeO diffusion, so that the La-silicate/Al<sub>2</sub>O<sub>3</sub> passivation films did not contain a considerable amount of Ge impurities. As can be understood from Figure 1e, SiO<sub>2</sub> appeared to have the highest barrier properties against diffusion of the GeO. Therefore, the small amount of GeO formed could not diffuse through the La-silicate layer when it was coated with SiO<sub>2</sub>. This must have suppressed the desorption reaction at the interface and the achieved electrical performance was optimum. This is in agreement with the study by Oh and Campbell, where they reported that the SiO<sub>2</sub> capping layer blocked the absorption of oxygen and prevented further oxidation of the Ge.<sup>29</sup> From these results, it is concluded that the deterioration of the C-V characteristics in the GeO<sub>2</sub>/Ge MOS capacitors originated from the interface reaction, driving volatilization of the GeO.

## V. CONCLUSIONS

Three approaches were taken in this work to improve the electrical performances of high-k La-based oxide films on Gesubstrates. They were increasing the Si concentration in the  $La_2O_3$  films, adopting an ultrathin  $Al_2O_3$  passivation layer at the La-silicate/Ge interface, and capping the La-silicate/ultrathin  $Al_2O_3$  gate stack layer with a 2-nm-thick SiO<sub>2</sub> layer. The electrical properties of the MOSCAPs were studied by the amount of hysteresis in their C-V curves, and the degradation in the  $V_{\rm FB}$  and  $D_{\rm it}$  using CVS tests. In general, increasing the Si concentration in the La-silicate films (up to 35%) was an effective method in improving the electrical performance. This was because suppression of the desorption reaction between the native GeO<sub>2</sub> and Ge substrate was induced by the lower diffusion of Ge (or GeO) through the La-silicate film, compared with pure La2O3. However, a Si concentration that was too high decreased the k value. Therefore, the Si concentration was fixed at 25%, and the interface with the Ge substrate was passivated with an ultrathin ALD Al<sub>2</sub>O<sub>3</sub> layer. The ALD process using TMA and O<sub>3</sub> induced two aspects in terms of the desorption reaction; TMA reduced the native GeO<sub>2</sub>, which suppressed the subsequent desorption reaction. In contrast, the prolonged ALD process induced adverse oxidation of Ge to GeO2, which eventually induced the desorption reaction. Therefore, two ALD cycles of Al<sub>2</sub>O<sub>3</sub> resulted in the optimal condition among the different cycle numbers that were attempted. The hysteresis in the C-V curves could be decreased to ~240 mV under this condition, while the Lasilicate films with no Al<sub>2</sub>O<sub>3</sub> passivation showed a hysteresis voltage of ~900 mV. The C–V hysteresis was further decreased to ~100 mV (best case 50 mV) by adopting a SiO<sub>2</sub> capping layer. This was believed to be caused by further suppression of the deleterious desorption reaction by almost completely suppressing the outward diffusion of GeO, which could have formed by the minute reaction between the O<sub>3</sub>-induced GeO<sub>2</sub> and Ge.

This work could provide a viable guideline in suppressing the C-V hysteresis by focusing on the possible routes to induce an adverse desorption reaction on Ge substrates for future MOSFETs. Although MOSFET fabrication includes various thermal treatments, which are not dealt with in this work, this work could also provide researchers with a viable reference to alleviate the adverse reaction that could be induced during the thermal treatment of the gate stack.

#### AUTHOR INFORMATION

#### **Corresponding Authors**

\*E-mail: cheolsh@snu.ac.kr.

\*E-mail: thinfilm@snu.ac.kr.

#### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work was supported by the Converging Research Center Program (2013K000158) through the Ministry of Science, ICT, and Future Planning, Republic of Korea, and also supported by Samsung Electronics. Co., Ltd. [Process development of Ge and III–V compound semiconductor for high mobility channel devices] and Samsung Display. Co., Ltd. [Fracture Analysis of an encapsulation layer for flexible OLED using electrical methods].

## REFERENCES

(1) Yamaguchi, T.; Lijima, R.; Ino, T.; Nishiyama, A.; Satake, H.; Fukushima, N. Additional Scattering Effects for Mobility Degradation in Hf-silicate Gate MISFETs. *IEDM Technol. Dig.* **2002**, 621–624.

(2) Kang, C. S.; Cho, H.-J.; Onishi, K.; Choi, R.; Nieh, R.; Goplan, S.; Krishnan, S.; Lee, J. C. Improved Thermal Stability and Device Performance of Ultra-thin (EOT<10Å) Gate Dielectric MOSFETs by using Hafnium Oxynitride (HfO<sub>x</sub>N<sub>y</sub>). *Symp. VLSI Technol., Dig. Tech. Pap.* **2002**, 146–147.

(3) Houssa, M.; Satta, A.; Simoen, E.; Jaeger, B. D.; Meuris, M.; Caymax, M.; Heyns, M. *Electrical Performance of Ge Devices, Germanium-Based Technologies*; Elsevier: Oxford, U. K., 2007.

(4) Kamata, Y. High-k/Ge MOSFETs for Future Nanoelectronics. *Mater. Today* **2008**, *11*, 30–38.

(5) Saraswat, K.; Chui, C. O.; Krishnamohan, T.; Kim, D. High Performance Germanium MOSFETs. *Mater. Sci. Eng. B* 2006, 135, 242–249.

(6) Shang, H.; Frank, M. M.; Gusev, E. P.; Chu, J. O.; Bedell, S. W.; Guarini, K. W.; Ieong, M. Germanium Channel MOSFETs: Opportunities and Challenges. *IBM J. Res. Dev* **2006**, *50*, 377–386.

(7) Prabhakaran, K.; Maeda, F.; Watanabe, Y.; Ogino, T. Distinctly Different Thermal Decomposition Pathways of Ultrathin Oxide Layer on Ge and Si Surfaces. *Appl. Phys. Lett.* **2000**, *76*, 2244–2246.

(8) Kita, K.; Suzuki, S.; Nomura, H.; Takahashi, T.; Nishimura, T.; Toriumi, A. Direct Evidence of GeO Volatilization from  $GeO_2/Ge$  and Impact of its Suppression on  $GeO_2/Ge$  Metal-Insulator-Semiconductor Characteristics. *Jpn. J. Appl. Phys.* **2008**, *47*, 2349–2353.

(9) Toriumi, A.; Tabata, T.; Hyun Lee, C.; Nishimura, T.; Kita, K.; Nagashio, K. Opportunities and Challenges for Ge CMOS - Control of Interfacing Field on Ge is a Key. *Microelectron. Eng.* **2009**, *86*, 1571–1576.

(10) Kita, K.; Takahashi, T.; Nomura, H.; Suzuki, S.; Nishimura, T.; Toriumi, A. Control of High-k/Germanium Interface Properties through Selection of High-k Materials and Suppression of GeO Volatilization. *Appl. Surf. Sci.* **2008**, *254*, 6100–6105.

(11) Wang, S. K.; Kita, K.; Lee, C. H.; Tabata, T.; Nishimura, T.; Nagashio, K.; Toriumi, A. Desorption Kinetics of GeO from GeO<sub>2</sub>/Ge Structure. *J. Appl. Phys.* **2010**, *108*, 054104.

(12) Sahle, C. J.; Sternemann, C.; Conrad, H.; Herdt, A.; Feroughi, O. M.; Tolan, M.; Hohl, A.; Wagner, R.; Lützenkirchen–Hecht, D.; Frahm, R.; Sakko, A.; Hämäläinen, K. Phase Separation and Nanocrystal Formation in GeO. *Appl. Phys. Lett.* **2009**, *95*, 021910.

(13) Kai Wang, S.; Liu, H.-G.; Toriumi, A. Kinetic Study of GeO Disproportionation into a  $GeO_2/Ge$  System using X-ray Photoelectron Spectroscopy. *Appl. Phys. Lett.* **2012**, *101*, 061907.

(14) Na, H. J.; Lee, J. C.; Heh, D.; Sivasubramani, P.; Kirsch, P. D.; Oh, J. W.; Majhi, P.; Rivillon, S.; Chabal, Y. J.; Lee, B. H.; Choi, R. Effective Surface Passivation Methodologies for High Performance Germanium Metal Oxide Semiconductor Field Effect Transistors. *Appl. Phys. Lett.* **2008**, *93*, 192115.

(15) Hymes, D. J.; Rosenberg, J. J. Growth and Materials Characterization of Native Germanium Oxynitride Thin Films on Germanium. J. Electrochem. Soc. **1988**, 135, 961–965.

(16) Xie, Q.; Deng, S.; Schaekers, M.; Lin, D.; Caymax, M.; Delabie, A.; Qu, X.-P.; Jiang, Y.-L.; Deduytsche, D.; Detavernier, C. Germanium Surface Passivation and Atomic Layer Deposition of High-k Dielectrics - A Tutorial Review on Ge-based MOS Capacitors. *Semicond. Sci. Technol.* **2012**, *27*, 074012.

(17) Iwauchi, S.; Tanaka, T. Interface Properties of  $Al_2O_3$ -Ge Structure and Characteristics of  $Al_2O_3$ -Ge MOS Transistors. Jpn. J. Appl. Phys. **1971**, 10, 260–265.

(18) Yu, D. S.; Chiang, K. C.; Cheng, C. F.; Chin, A.; Zhu, C.; Li, M. F.; Kwong, D.-L. Fully Silicided NiSi:Hf-LaAlO<sub>3</sub>/SG-GOI n-MOSFETs with High Electron Mobility. *IEEE Electron Device Lett.* **2004**, *25*, 559–562.

(19) Xie, Q.; Deduytsche, D.; Schaekers, M.; Caymax, M.; Delabie, A.; Quc, X.-P.; Detavernier, C. Effective Electrical Passivation of Ge(100) for HfO<sub>2</sub> Gate Dielectric Layers using O<sub>2</sub> Plasma. *Electochem.* Solid-State Lett. **2011**, 14, G20–G22.

(20) Lee, C. H.; Tabata, T.; Nishimura, T.; Nagashio, K.; Kita, K.; Toriumi, A. Ge/GeO<sub>2</sub> Interface Control with High-Pressure Oxidation for Improving Electrical Characteristics. *Appl. Phys. Exp.* **2009**, *2*, 071404.

(21) Cheng, C.-C.; Chiena, C.-H.; Luo, G.-L.; Yang, C.-H.; Kuo, M.-L.; Lin, J.-H.; Chang, C.-Y. Ultrathin Si Capping Layer Suppresses Charge Trapping in  $HfO_xN_y/Ge$  Metal-Insulator-Semiconductor Capacitors. *Appl. Phys. Lett.* **2007**, *90*, 012905.

(22) Hattangady, S. V.; Fountain, G. G.; Rudder, R. A.; Mantini, M. J.; Vitkavage, D. J.; Markunas, R. J. Interface Engineering with Pseudormorphic Interlayers: Ge Metal-Insulator-Semiconductor Structures. *Appl. Phys. Lett.* **1990**, *57*, 581–583.

(23) Tiwari, S.; Wright, S. L.; Batey, J. Unpinned GaAs MOS capacitors and transistors. *IEEE Electron Device Lett.* **1988**, *9*, 488–490.

(24) Wu, N.; Zhang, Q.; Zhu, C.; Chan, D. S. H.; Du, A.; Balasubramanian, N.; Li, M. F.; Sin, J. K. O.; Kwong, D. L. A TaN-HfO<sub>2</sub>-Ge pMOSFET with Novel SiH<sub>4</sub> Surface Passivation. *IEEE Electron Device Lett.* **2004**, 25, 631–633.

(25) Houssa, M.; Pourtois, G.; Caymax, M.; Meuris, M.; Heyns, M.M. First-Principles Study of the Structural and Electronic Properties of (100) GeGe (M)O<sub>2</sub> Interfaces (M=Al, La, or Hf). *Appl. Phys. Lett.* **2008**, *92*, 242101.

(26) Kato, K.; Kyogoku, S.; Sakashita, M.; Takeuchi, W.; Kondo, H.; Takeuchi, S.; Nakatsuka, O.; Zaima, S. Control of Interfacial Properties of Al<sub>2</sub>O<sub>3</sub>/Ge Gate Stack Structure using Radical Nitridation Technique. *Jpn. J. Appl. Phys.* **2011**, *50*, 10–17.

(27) Jung, H.-S.; Yu, I.-H.; Kim, H. K.; Lee, S. Y.; Lee, J.; Choi, Y. J.; Chung, Y. J.; Lee, N.-I.; Park, T. J.; Choi, J.-H.; Hwang, C. S. Reduction of Charge Trapping in HfO<sub>2</sub> Film on Ge Substrates by Atomic Layer Deposition of Various Passivating Interfacial Layers. *IEEE Trans. Electron Device* **2012**, *59*, 2350–2356. (28) Prabhakaran, K.; Ogino, T. Oxidation of Ge(100) and Ge(111)

Surfaces: An UPS and XPS Study. *Surface Science* 1995, 325, 263–271.

(29) Oh, J.; Campbell, J. C. Thermal Desorption of Ge Native Oxides and the Loss of Ge fom the Surface. J. Electron. Mater. 2004, 33, 364–367.

(30) Li, H. J.; Gardner, M. I. Dual High-k Gate Dielectric with Poly Gate Electrode: HfSiON on nMOS and  $Al_2O_3$  Capping Layer on pMOS. *IEEE Electron. Device Lett.* **2005**, *26*, 441–444.

(31) Lin, L.; Robertson, J. Atomic Mechanism of Flat-band Voltage Shifts at  $La_2O_3$ ,  $Al_2O_3$  and  $Nb_2O_5$  Capping Layers. *Microelectron. Eng.* **2009**, *86*, 1743–1746.

(32) Hinkle, C. L.; Sonnet, A. M.; Vogel, E. M.; McDonnell, S.; Hughes, G. J.; Milojevic, M.; Lee, B.; Aguirre-Tostado, F. S.; Choi, K. J.; Kim, H. C.; Kim, J.; Wallace, R. M. GaAs Interfacial Self-Cleaning by Atomic Layer Deposition. *Appl. Phys. Lett.* **2008**, *92*, 071901.

(33) Milojevic, M.; Contreras-Guerrero, R.; Lopez-Lopez, M.; Kim, J.; Wallace, R. M. Characterization of the "Clean-up" of the Oxidized Ge(100) Surface by Atomic Layer Deposition. *Appl. Phys. Lett.* **2009**, *95*, 212902.

(34) Park, T. J.; Kim, J. H.; Seo, M. H.; Jang, J. H.; Hwang, C. S. Improvement of Thermal Stability and Composition Changes of Atomic Layer Deposited HfO2 on Si by in situ  $O_3$  Pretreatment. *Appl. Phys. Lett.* **2007**, *90*, 152906.